# NuDAQ<sup>ò</sup> PCI-7348/7396

48/96-CH Digital I/O Cards DIN-96DI, DIN-96DO User's Guide

©Copyright 2002 ADLINK Technology Inc.

All Rights Reserved.

Manual Rev. 1.22 June 7, 2002

Pato No: 50-11107-200

The information in this document is subject to change without prior notice in order to improve reliability, design and function and does not represent a commitment on the part of the manufacturer.

In no event will the manufacturer be liable for direct, indirect, special, incidental, or consequential damages arising out of the use or inability to use the product or documentation, even if advised of the possibility of such damages.

This document contains proprietary information protected by copyright. All rights are reserved. No part of this manual may be reproduced by any mechanical, electronic, or other means in any form without prior written permission of the manufacturer.

#### **Trademarks**

$\mbox{NuDAQ}^{\mbox{\tiny B}},\mbox{ DAQBench}^{\mbox{\tiny B}}$  are registered trademarks of ADLINK Technology Inc.

Other product names mentioned herein are used for identification purposes only and may be trademarks and/or registered trademarks of their respective companies.

# Getting service from ADLINK

Customer Satisfaction is always the most important thing for ADLINK Tech Inc. If you need any help or service, please contact us and get it.

|                 | ADLINK Technology Inc.    |        |                                |  |  |

|-----------------|---------------------------|--------|--------------------------------|--|--|

| Web Site        | http://www.adlinktech.com |        |                                |  |  |

| Sales & Service | service@adlinktech.com    |        |                                |  |  |

|                 | NuDAQ                     | nudad  | q@adlinktech.com               |  |  |

| Technical       | automation                | auton  | nation@adlinktech.com          |  |  |

| Support         | NuIPC                     | nuipc  | @adlinktech.com                |  |  |

|                 | NuPRO/EBC                 | nupro  | @adlinktech.com                |  |  |

| TEL             | +886-2-82265877           | FAX    | +886-2-82265717                |  |  |

| Address         | 9F, No. 166, Jian Yi Road | , Chur | ngho City, Taipei, 235 Taiwan, |  |  |

Please inform or FAX us of your detailed information for a prompt, satisfactory and constant service.

|                          | Detailed Company Information                                                     |

|--------------------------|----------------------------------------------------------------------------------|

| Company/Organization     |                                                                                  |

| Contact Person           |                                                                                  |

| E-mail Address           |                                                                                  |

| Address                  |                                                                                  |

| Country                  |                                                                                  |

| TEL                      | FAX                                                                              |

| Web Site                 |                                                                                  |

| Questions                |                                                                                  |

| Product Model            |                                                                                  |

| Environment to Use       | OS: Computer M/B: CPU: Chipset: BIOS: Video Card: Network Interface Card: Other: |

| Challenge Description    |                                                                                  |

| Suggestions to<br>ADLINK |                                                                                  |

# **Table of Contents**

| Gilapi                                                                                    | er 1 Introduction                                                                                                                                                                                                                                                                                                            |                     |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 1.1                                                                                       | Features                                                                                                                                                                                                                                                                                                                     | 1                   |

| 1.1.                                                                                      |                                                                                                                                                                                                                                                                                                                              |                     |

| 1.1.                                                                                      | 2 Timer / Counter and Interrupt System                                                                                                                                                                                                                                                                                       | 2                   |

| 1.1.                                                                                      | 3 Miscellaneous                                                                                                                                                                                                                                                                                                              | 2                   |

| 1.2                                                                                       | Applications                                                                                                                                                                                                                                                                                                                 | 2                   |

| 1.3                                                                                       | Specifications                                                                                                                                                                                                                                                                                                               | 3                   |

| 1.4                                                                                       | Software Supporting                                                                                                                                                                                                                                                                                                          | 4                   |

| 1.4.                                                                                      |                                                                                                                                                                                                                                                                                                                              | 4                   |

| 1.4.                                                                                      |                                                                                                                                                                                                                                                                                                                              |                     |

| 1.4.                                                                                      |                                                                                                                                                                                                                                                                                                                              | 5                   |

| 1.4.                                                                                      | 4 DAQBench™: ActiveX Controls                                                                                                                                                                                                                                                                                                | 5                   |

| 1.4.                                                                                      |                                                                                                                                                                                                                                                                                                                              | 5                   |

| 1.4.                                                                                      | 6 PCIS-ISG: ISaGRAF <sup>IM</sup> driver                                                                                                                                                                                                                                                                                     | 5                   |

| 1.4.                                                                                      |                                                                                                                                                                                                                                                                                                                              |                     |

| 1.4.                                                                                      | 8 PCIS-OPC: OPC Server                                                                                                                                                                                                                                                                                                       | 6                   |

| Chapt                                                                                     | er 2 Installation                                                                                                                                                                                                                                                                                                            | 7                   |

| 0.4                                                                                       | M/h = ( M = - 1 I =                                                                                                                                                                                                                                                                                                          | _                   |

| 2.1                                                                                       | What You Have                                                                                                                                                                                                                                                                                                                | 7                   |

| 2.1                                                                                       |                                                                                                                                                                                                                                                                                                                              |                     |

|                                                                                           | UnpackingPCI-7396 Layout                                                                                                                                                                                                                                                                                                     | 8                   |

| 2.2                                                                                       | Unpacking                                                                                                                                                                                                                                                                                                                    |                     |

| 2.2<br>2.3                                                                                | Unpacking PCI-7396 Layout Hardware Installation Outline Connectors' Pin Assignment of PCI-7348                                                                                                                                                                                                                               | 8<br>10<br>11       |

| 2.2<br>2.3<br>2.4                                                                         | Unpacking PCI-7396 Layout Hardware Installation Outline Connectors' Pin Assignment of PCI-7348                                                                                                                                                                                                                               | 8<br>10<br>11       |

| 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7                                                    | Unpacking PCI-7396 Layout Hardware Installation Outline Connectors' Pin Assignment of PCI-7348 Jumpers' Description                                                                                                                                                                                                          | 8<br>10<br>11<br>12 |

| 2.2<br>2.3<br>2.4<br>2.5<br>2.6                                                           | Unpacking PCI-7396 Layout Hardware Installation Outline Connectors' Pin Assignment of PCI-7348 Jumpers' Description                                                                                                                                                                                                          |                     |

| 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7                                                    | Unpacking PCI-7396 Layout Hardware Installation Outline Connectors' Pin Assignment of PCI-7348 Connectors' Pin Assignment of PCI-7396 Jumpers' Description  1 Power-on-state Termination Boards Supporting                                                                                                                   |                     |

| 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.7                                             | Unpacking PCI-7396 Layout                                                                                                                                                                                                                                                                                                    |                     |

| 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.7<br>2.8<br>2.8.                              | Unpacking PCI-7396 Layout Hardware Installation Outline Connectors' Pin Assignment of PCI-7348 Connectors' Pin Assignment of PCI-7396 Jumpers' Description  1 Power-on-state Termination Boards Supporting 1 Connect with DIN-100S 2 Connect with DIN-96DI                                                                   |                     |

| 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.7.<br>2.8<br>2.8.                             | Unpacking PCI-7396 Layout Hardware Installation Outline Connectors' Pin Assignment of PCI-7348 Connectors' Pin Assignment of PCI-7396 Jumpers' Description  1 Power-on-state Termination Boards Supporting 1 Connect with DIN-100S 2 Connect with DIN-96DI                                                                   |                     |

| 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.7<br>2.8<br>2.8<br>2.8.                       | Unpacking PCI-7396 Layout Hardware Installation Outline Connectors' Pin Assignment of PCI-7348 Connectors' Pin Assignment of PCI-7396 Jumpers' Description  1 Power-on-state Termination Boards Supporting 1 Connect with DIN-100S 2 Connect with DIN-96DI                                                                   |                     |

| 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.7<br>2.8<br>2.8<br>2.8.                       | Unpacking PCI-7396 Layout Hardware Installation Outline Connectors' Pin Assignment of PCI-7348 Connectors' Pin Assignment of PCI-7396 Jumpers' Description 1 Power-on-state Termination Boards Supporting 1 Connect with DIN-100S 2 Connect with DIN-96DI 3 Connect with DIN-96DO                                            |                     |

| 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.7<br>2.8<br>2.8<br>2.8.<br>2.8.               | Unpacking PCI-7396 Layout Hardware Installation Outline Connectors' Pin Assignment of PCI-7348 Connectors' Pin Assignment of PCI-7396 Jumpers' Description 1 Power-on-state Termination Boards Supporting 1 Connect with DIN-100S 2 Connect with DIN-96DI 3 Connect with DIN-96DO  ter 3 Registers Format                    |                     |

| 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.7<br>2.8<br>2.8<br>2.8<br>2.8.<br>2.8.<br>3.1 | Unpacking PCI-7396 Layout Hardware Installation Outline Connectors' Pin Assignment of PCI-7348 Connectors' Pin Assignment of PCI-7396 Jumpers' Description  1 Power-on-state Termination Boards Supporting 1 Connect with DIN-100S 2 Connect with DIN-96DI 3 Connect with DIN-96DO  cer 3 Registers Format PCI PnP Registers |                     |

| 3.5 External Trigger Enable Register        | 19 |

|---------------------------------------------|----|

| 3.6 External Trigger Disable Register       |    |

| 3.7 Change of State (COS) Control Register  | 20 |

| 3.8 Interrupt Source Control (ISC) Register |    |

| 3.9 Clear Interrupt Register                |    |

| 3.10 Timer/Counter Register                 |    |

| 3.11 High Level Programming                 |    |

| Chapter 4 Operation Theorem                 | 23 |

| 4.1 Digital I/O Ports                       | 23 |

| 4.1.1 Introduction                          |    |

| 4.1.2 External Trigger                      | 23 |

| 4.2 8254 Timer/Counter Operation            | 25 |

| 4.2.1 Introduction                          |    |

| 4.2.2 Cascaded 32 bits Timer                |    |

| 4.2.3 Event Counter and Edge Control        |    |

| 4.3 Interrupt Circuit                       |    |

| 4.3.1 System Architecture                   |    |

| 4.3.2 IRQ Level Setting                     |    |

| 4.3.3 Dual Interrupt System                 |    |

| 4.3.4 Interrupt Source Control (ISC)        |    |

| 4.3.5 Change of State (COS) Interrupt       |    |

| 4.4 12V and 5V Power Supply                 | 30 |

| Chapter 5 C/C++ Libraries                   | 31 |

| 5.1 Libraries Installation                  | 31 |

| 5.2 Programming Guide                       | 32 |

| 5.2.1 Naming Convention                     |    |

| 5.2.2 Data Types                            | 32 |

| 5.3 _7396_Initial                           | 33 |

| 5.4 _7396_DI                                | 34 |

| 5.5 _7396_DO                                | 36 |

| 5.6 _7396_Config_Port                       | 37 |

| 5.7 _7396_Software_Reset                    |    |

| 5.8 _7396_INT_Source_Control                |    |

| 5.9 _7396_COSIRQ_Control                    | 41 |

| 5.10 _7396_CLR_IRQ                          | 42 |

| 5.11 _7396_Set_Event_Edge                   | 43 |

| 5.12 _7396_Cascaded_Timer                   |    |

| 5.13 7396 Timer Start                       | 45 |

| 5.14                 | _7396_Timer_Read                      | 46             |

|----------------------|---------------------------------------|----------------|

| Appen                | dix 1 DIN-96DI                        | 47             |

| A1.1                 | Introductions                         |                |

| A1.2                 | Features                              | 47             |

| A1.3                 | Specifications                        | 47             |

| A1.4                 | Layout of DIN-96DI                    | 49             |

| A1.5                 | DI Circuits and Wiring                | 50             |

|                      |                                       |                |

| <b>Appen</b>         | dix 2 DIN-96DO                        | 51             |

| Appen<br>A2.1        | Introductions                         |                |

| • •                  |                                       | 51             |

| A2.1                 | IntroductionsFeatures                 | 51<br>51       |

| A2.1<br>A2.2         | Introductions                         | 51<br>51<br>51 |

| A2.1<br>A2.2<br>A2.3 | Introductions Features Specifications | 51<br>51<br>51 |

# How to Use This Guide

This manual is designed to help you use the PCI-7396. It describes how to modify and control various functions on the PCI-7396 card to meet your requirements. It is divided into three chapters:

- ◆ Chapter 1, "Introduction," gives an overview of the product features. applications, and specifications.

- ◆ Chapter 2, "Installation," describes how to install the PCI-7396. The layout of PCI-7396 is shown. The jumper settings, the connectors' pin assignment, and the other notes for installation are described.

- Chapter 3, "Registers' Format," describes the details of registers' format and structure of the PCI-7396, this information is very important for the programmers who want to control the hardware by low-level programming language.

- Chapter 4, "Operation Theorem" describes more details about the versatile functions, including DIO, timer / counter, and interrupt systems.

- ◆ Chapter 5, "C/C++ Software Libraries" specifies the software libraries of C/C++ language under DOS environment that make you operate the functions of this card easily.

# Introduction

The PCI-7396 is a 48/96-bit parallel digital input/output (DIO) card designed for industrial applications. The plug and play feature of PCI-Bus architecture make it easy for users to install their systems quickly.

The PCI-7396 emulates two/four 8255 Programmable Peripheral Interface (PPI) chips. Each PPI offers 3 8-bit DIO ports which can be accessed simultaneously. The total 6/12 ports can be programmed as input or output independently.

The PCI-7396 supports external trigger to latch the digital input data. The function of "Change of State" (COS) interrupt is provided. It means when anyone of these digital inputs changes its state, an interrupt will be generated for user to handle this external event.

### 1.1 Features

The PCI-7396 Digital I/O boards provide the following advanced features:

### 1.1.1 Digital I/O Ports

- ◆ 48/96 TTL compatible digital I/O lines

- ◆ SCSI-type 100-pin connector (AMP-787082-9)

- ◆ 48mA High current driving capability per channel

- Output status read-back

- Support external trigger to latch digital input data (PCI-7348 only)

### 1.1.2 Timer / Counter and Interrupt System

- ◆ A programmable 32-bit timer to generate timer interrupt

- ◆ A programmable 16-bit event counter to generate event interrupt

- ♦ 48/96-bit change of state (COS) interrupt

- Dual interrupt system

### 1.1.3 Miscellaneous

- Provide 12V and 5V power supply on SCSI-type 100-pin connectors(only for PCI-7348)

- On board resettable fuses to protect power supply from external damage. (only for PCI-7348)

## 1.2 Applications

- ◆ Programmable mixed digital input & output

- ◆ Industrial monitoring and controlling

- LED indicator driving

- Parallel data transfer

- ◆ TTL,DTL, and CMOS logic sensing

### 1.3 Specifications

I/O channels 48-bit for PCI-7348

96-bit for PCI-7396

Input Signal Logic High Voltage : 2.0 V to 5.25V

Logic Low Voltage : 0.0 V to 0.80V

Logic High Current : 0.1 uA Logic Low Current : -8 mA

Output Signal Logic High Voltage : Typical 3.3 V

: Minimum 2.4 V

Logic Low Voltage : Maximum 0.5V Logic High Current : -15.0 mA

Logic Low Current : 48.0 mA

Operating Temperature  $0^{\circ} \sim 60^{\circ} \text{ C}$ Storage Temperature  $-20^{\circ} \sim 80^{\circ} \text{ C}$

Humidity 5% ~ 95% non-condensing I/O Connectors 100-pin SCSI connector

Bus PCI bus, rev 2.1 IRQ Level Set by PCI BIOS I/O port address Set by PCI BIOS

Power Consumption PCI-7348 : 350mA (TYP) (without external devices) PCI-7396 : 450mA (TYP) Transfer Rate 1M bytes/sec (Typical)

Size Half-size PCB: 158 mm x 107 mm

### 1.4 Software Supporting

ADLink provides versatile software drivers and packages for users' different approach to built-up a system. We not only provide programming library such as DLL for many Windows systems, but also provide drivers for many software package such as LabVIEW<sup>®</sup>, HP VEE<sup>TM</sup>, DASYLab<sup>TM</sup>, InTouch<sup>TM</sup>, InControl<sup>TM</sup>, ISaGRAF<sup>TM</sup>, and so on.

All the software options are included in the ADLink CD. The non-free software drivers are protected with serial licensed code. Without the software serial number, you can still install them and run the demo version for two hours for demonstration purpose. Please contact with your dealer to purchase the formal license serial code.

### 1.4.1 Programming Library

For customers who are writing their own programs, we provide function libraries for many different operating systems, including:

- ◆ **DOS** Library: Borland C/C++ and Microsoft C++, the functions descriptions are included in this user's guide.

- ♦ Windows 95 DLL: For VB, VC++, Delphi, BC5, the functions descriptions are included in this user's guide.

- ◆ PCIS-DASK: Include device drivers and DLL for Windows 98, Windows NT and Windows 2000. DLL is binary compatible across Windows 98, Windows NT and Windows 2000. That means all applications developed with PCIS-DASK are compatible across Windows 98, Windows NT and Windows 2000. The developing environment can be VB, VC++, Delphi, BC5, or any Windows programming language that allows calls to a DLL. The user's guide and function reference manual of PCIS-DASK are in the CD. Please refer the PDF manual files under (\Manual PDF\Software\PCIS-DASK)

- ◆ PCIS-DASK/X: Include device drivers and shared library for **Linux**. The developing environment can be Gnu C/C++ or any programming language that allows linking to a shared library. The user's guide and function reference manual of PCIS-DASK/X are in the CD. (\Manual PDF\Software\PCIS-DASK-X.)

The above software drivers are shipped with the board. Please refer to the "Software Installation Guide" to install these drivers.

### 1.4.2 PCIS-LVIEW: LabVIEW<sup>®</sup> Driver

PCIS-LVIEW contains the VIs, which are used to interface with NI's LabVIEW® software package. The PCIS-LVIEW supports Windows 95/98/NT/2000. The LabVIEW® drivers are free shipped with the board. You can install and use them without license. For detail information about PCIS-LVIEW, please refer to the user's guide in the CD.

(\Manual\_PDF\Software\PCIS-LVIEW)

#### 1.4.3 PCIS-VEE: HP-VEE Driver

The PCIS-VEE includes the user objects, which are used to interface with HP VEE software package. PCIS-VEE supports Windows 95/98/NT. The HP-VEE drivers are free shipped with the board. You can install and use them without license. For detail information about PCIS-VEE, please refer to the user's guide in the CD.

(\Manual\_PDF\Software\PCIS-VEE)

### 1.4.4 DAQBench™: ActiveX Controls

We suggest the customers who are familiar with ActiveX controls and VB/VC++ programming use the DAQBench<sup>TM</sup> ActiveX Control components library for developing applications. The DAQBench<sup>TM</sup> is designed under Windows NT/98. For more detailed information about DAQBench, please refer to the user's guide in the CD.

(\Manual\_PDF\Software\DAQBench\DAQBench Manual.PDF)

### 1.4.5 PCIS-DDE: DDE Server and InTouch™

DDE stands for Dynamic Data Exchange specifications. The PCIS-DDE includes the PCI cards' DDE server. The PCIS-DDE server is included in the ADLINK CD. It needs license. The DDE server can be used conjunction with any DDE client under Windows NT.

### 1.4.6 PCIS-ISG: ISaGRAF<sup>™</sup> driver

The ISaGRAF WorkBench is an IEC1131-3 SoftPLC control program development environment. The PCIS-ISG includes ADLink products' target drivers for ISaGRAF under Windows NT environment. The PCIS-ISG is included in the ADLINK CD. It needs license.

# 1.4.7 PCIS-ICL: InControl<sup>™</sup> Driver

PCIS-ICL is the InControl driver which support the Windows NT. The PCIS-ICL is included in the ADLINK CD. It needs license.

### 1.4.8 PCIS-OPC: OPC Server

PCIS-OPC is an OPC Server, which can link with the OPC clients. There are many software packages on the market can provide the OPC clients now. The PCIS-OPC supports the Windows NT. It needs license.

# Installation

This chapter describes how to install the PCI-7396. The contents in the package and unpacking information that you should be careful are described.

Please follow the steps to install the PCI-7348/7396.

- ◆ Check what you have (section 2.1)

- ◆ Unpacking (section 2.2)

- ♦ Check the PCB (section 2.3)

- ♦ Install the hardware (section 2.4)

- Please refer to the "Software Installation Guide" to install the software drivers.

### 2.1 What You Have

In addition to this *User's Manual*, the package includes the following items:

- PCI-7396 96-bits Parallel Digital I/O Card

- ADLINK CD

- Software Installation Guide

If any of these items is missing or damaged, contact the dealer from whom you purchased the product. Save the shipping materials and carton in case you want to ship or store the product in the future.

### 2.2 Unpacking

Your PCI-7396 card contains sensitive electronic components that can be easily damaged by static electricity.

The card should be done on a grounded anti-static mat. The operator should be wearing an anti-static wristband, grounded at the same point as the anti-static mat.

Inspect the card module carton for obvious damage. Shipping and handling may cause damage to your module. Be sure there are no shipping and handling damages on the module before processing.

After opening the card module carton, exact the system module and place it only on a grounded anti-static surface component side up.

Note: DO NOT APPLY POWER TO THE CARD IF IT HAS BEEN DAMAGED.

You are now ready to install your PCI-7396.

## 2.3 PCI-7396 Layout

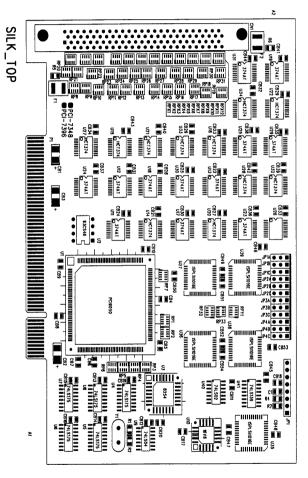

Figure 2.1 PCI-7396 Layout

#### 2.4 Hardware Installation Outline

#### Hardware configuration

The PCI cards (or CompactPCI cards) are equipped with plug and play PCI controller, it can request base addresses and interrupt according to PCI standard. The system BIOS will install the system resource based on the PCI cards' configuration registers and system parameters (which are set by system BIOS). Interrupt assignment and memory usage (I/O port locations) of the PCI cards can be assigned by system BIOS only. These system resource assignments are done on a board-by-board basis. It is not suggested to assign the system resource by any other methods.

#### PCI slot selection

The PCI card can be inserted to any PCI slot without any configuration for system resource.

#### Installation Procedures

- 1 Turn off your computer

- 2 Turn off all accessories (printer, modem, monitor, etc.) connected to your computer.

- 3 Remove the cover from your computer.

- 4 Setup jumpers on the PCI or CompactPCI card.

- 5 Select a 32-bit PCI slot. PCI slot are short than ISA or EISA slots, and are usually white or ivory.

- 6 Before handling the PCI cards, discharge any static buildup on your body by touching the metal case of the computer. Hold the edge and do not touch the components.

- 7 Position the board into the PCI slot you selected.

- 8 Secure the card in place at the rear panel of the system.

### 2.5 Connectors' Pin Assignment of PCI-7348

The I/O pin assignment of PCI-7348 is shown in the Figure 2.2.

| (1)  | P1A0 | (26) P2A0 | (51) EVENT |

|------|------|-----------|------------|

| (2)  | P1A1 | (27) P2A1 | (52) GND   |

| (3)  | P1A2 | (28) P2A2 | (53) GND   |

| (4)  | P1A3 | (29) P2A3 | (54) GND   |

| (5)  | P1A4 | (30) P2A4 | (55) GND   |

| (6)  | P1A5 | (31) P2A5 | (56) GND   |

| (7)  | P1A6 | (32) P2A6 | (57) GND   |

| (8)  | P1A7 | (33) P2A7 | (58) GND   |

| (9)  | P1B0 | (34) P2B0 | (59) GND   |

| (10) | P1B1 | (35) P2B1 | (60) GND   |

| (11) | P1B2 | (36) P2B2 | (61) GND   |

| (12) | P1B3 | (37) P2B3 | (62) GND   |

| (13) | P1B4 | (38) P2B4 | (63) GND   |

| (14) | P1B5 | (39) P2B5 | (64) GND   |

| (15) | P1B6 | (40) P2B6 | (65) GND   |

| (16) | P1B7 | (41) P2B7 | (66) GND   |

| (17) | P1C0 | (42) P2C0 | (67) GND   |

| (18) | P1C1 | (43) P2C1 | (68) GND   |

| (19) | P1C2 | (44) P2C2 | (69) GND   |

| (20) | P1C3 | (45) P2C3 | (70) GND   |

| (21) | P1C4 | (46) P2C4 | (71) GND   |

| (22) | P1C5 | (47) P2C5 | (72) GND   |

| (23) | P1C6 | (48) P2C6 | (73) GND   |

| (24) | P1C7 | (49) P2C7 | (74) GND   |

| (25) | V5V  | (50) +12V | (75) V5V   |

|      |      |           |            |

(94) GND (95) GND (96) GND (97) GND (98) GND (99) EXTTRG (100) +12V

(76) GND

(77) GND

(78) GND (79) GND (80) GND (81) GND (82) GND (83) GND (84) GND (85) GND (86) GND (87) GND (88) GND (89) GND (90) GND (91) GND (92) GND (93) GND

The DIO pin names are specified as PnXb, where

n : means the PPI number of the PCI-7348, n=1~2 X : means the port name of the PPI, X='A', 'B' or 'C'

b: means the bit number of the port, b=0~7 For example, P1C4 means bit 4 of port C on PPI1.

**EXTTRG**: External trigger signal to latch digital input data

**EVENT**: External event source for counter 0

V5V : +5V power supply output+12V : +12v power supply output

GND : Ground

**Note**: The power supply pins are protected by resettable fuses. Refer

to section 4.4 for details of the power supply.

# 2.6 Connectors' Pin Assignment of PCI-7396

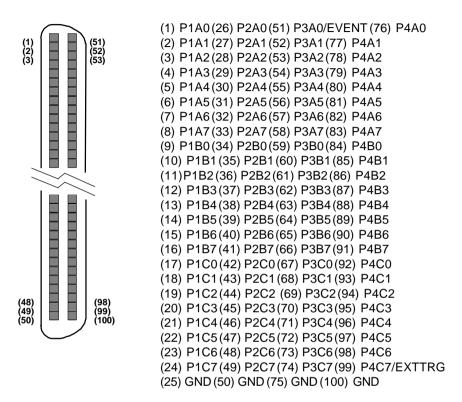

Figure 2.3 Connectors Pin Assignment of PCI-7396

The DIO pin names are specified as *PnXb*, where

n: means the PPI number of the PCI-7396, n=1~4

X: means the port name of the PPI, X= 'A', 'B' or 'C'

b: means the bit number of the port, b=0~7

For example, P1C4 means bit 4 of port C on PPI1.

EXTTRG: External trigger signal to latch digital input data

EVENT: External event source for counter 0

GND: Ground

### 2.7 Jumpers' Description

The PCI-7396 is a 'plug and play' add-on card using PCI bus. It is unnecessary for user to setup its base address and IRQ level to fit the hardware of your computer system. However, to fit users' versatile operation, there are still a few jumpers to set the power-on-states of all I/O ports.

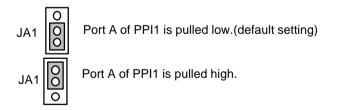

#### 2.7.1 Power-on-state

For all I/O ports of the PCI-7396, the power-on-states could be pulled high, pulled low, or floating. It is depended on the jumper settings. Table 2.1 lists the reference numbers of jumpers and their corresponding port names.

| Jumper | Port Name | Jumper | Port Name |

|--------|-----------|--------|-----------|

| JA1    | P1A       | JA3    | P3A       |

| JB1    | P1B       | JB3    | P3B       |

| JC1    | P1C       | JC3    | P3C       |

| JA2    | P2A       | JA4    | P4A       |

| JB2    | P2B       | JB4    | P4B       |

| JC2    | P2C       | JC4    | P4C       |

Table 2.1 Jumpers and port names list

All the jumpers are identical physically. The power-on-state of each port can be set independently. To pull all signals low is the default settings. The following diagram use JA1 as an example to show the possible settings.

When the jumper cap is removed, the power-on-state is floating.

## 2.8 Termination Boards Supporting

PCI-7396 can be connected with several different daughter boards, including DIN-100S, DIN-96DI, and DIN-96DO. The functionality and connections are specified as follows.

#### 2.8.1 Connect with DIN-100S

DIN-100S is a direct connector for the add-on card that is equipped with SCSI-100 connector. It is suitable for the simple applications that do not need isolated connection in front of the digital inputs or outputs of PCI-7396.

#### 2.8.2 Connect with DIN-96DI

DIN-96DI digital input termination board features high-voltage opto-isolation on all inputs to prevent floating potential and ground loop problems from damaging your PC system. It is composed of one TB-96 base board, one TB-96DI daughter board, and one DIN socket for easy maintenance, wiring, and installation. It provides 96 channels that are accessed through a SCSI-100 connector.(see Appendix A1)

#### 2.8.3 Connect with DIN-96DO

DIN-96DO digital output termination board features high-voltage optoisolation on all outputs to prevent floating potential and ground loop problems from damaging your PC system. It is composed of one TB-96 base board, one TB-96DO daughter board, and one DIN socket for easy maintenance, wiring, and installation. It provides 96 channels that are accessed through a SCSI-100 connector. (see Appendix A2).

# Registers Format

The detailed descriptions of the registers format are specified in this chapter. This information is quite useful for the programmers who wish to handle the card by low-level programming. However, we suggest user have to understand more about the PCI interface then start any low-level programming. In addition, the contents of this chapter can help users understand how to use software driver to manipulate this card.

### 3.1 PCI PnP Registers

This PCI card functions as a 32-bit PCI target device to any master on the PCI bus. There are three types of registers: PCI Configuration Registers (PCR), Local Configuration Registers (LCR) and PCI-6308 registers.

The PCR, which is compliant to the PCI-bus specifications, is initialized and controlled by the plug & play (PnP) PCI BIOS. User's can study the PCI BIOS specification to understand the operation of the PCR. Please contact with PCISIG to acquire the specifications of the PCI interface.

The PCI bus controller PCI-9050 is provided by PLX technology Inc. (www.plxtech.com). For more detailed information of LCR, please visit PLX technology's web site to download relative information. It is not necessary for users to understand the details of the LCR if you use the software library. The PCI PnP BIOS assigns the base address of the LCR. The assigned address is located at offset 14h of PCR.

The PCI-6308 registers are shown in the next section. The base address, which is also assigned by the PCI PnP BIOS, is located at offset 18h of PCR. Therefore, users can read the 18h of PCR to know the base address by using the BIOS function call.

| Please do not try to modify the base address an by the PCI PnP BIOS, it may cause resource conf | d interrupt which assigned liction in your system. |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------|

|                                                                                                 |                                                    |

|                                                                                                 |                                                    |

|                                                                                                 |                                                    |

|                                                                                                 |                                                    |

|                                                                                                 |                                                    |

|                                                                                                 |                                                    |

|                                                                                                 |                                                    |

|                                                                                                 |                                                    |

|                                                                                                 |                                                    |

|                                                                                                 |                                                    |

|                                                                                                 |                                                    |

|                                                                                                 |                                                    |

|                                                                                                 |                                                    |

|                                                                                                 |                                                    |

# 3.2 I/O Address Map

Most of the PCI-7396 registers are 32 bits. The users can access these registers by 32 bits I/O instructions. The following table shows the registers map, including descriptions and their offset addresses relative to the base address.

| Offset | Write                         | Read                      |

|--------|-------------------------------|---------------------------|

| 0x00   | P1ABC                         | P1ABC                     |

| 0x04   | P1Control                     | No used                   |

| 0x08   | P1EXTTRG Enable               | No used                   |

| 0x0C   | P1EXTTRG Disable              | No used                   |

| 0x10   | P2ABC                         | P2ABC                     |

| 0x14   | P2Control                     | No used                   |

| 0x18   | P2EXTTRG Enable               | No used                   |

| 0x1C   | P2EXTTRG Disable              | No used                   |

| 0x20   | P3ABC                         | P3ABC                     |

| 0x24   | P3Control                     | No used                   |

| 0x28   | P3EXTTRG Enable               | No used                   |

| 0x2C   | P3EXTTRG Disable              | No used                   |

| 0x30   | P4ABC                         | P4ABC                     |

| 0x34   | P4Control                     | No used                   |

| 0x38   | P4EXTTRG Enable               | No used                   |

| 0x3C   | P4EXTTRG Disable              | No used                   |

| 0x40   | Timer/Counter #0              | Timer/Counter #0          |

| 0x44   | Timer/Counter #1              | Timer/Counter #1          |

| 0x48   | Timer/Counter #2              | Timer/Counter #2          |

| 0x4C   | Timer/Counter Mode Control    | Timer/Counter Mode Status |

| 0x50   | ISC: Interrupt Source Control | No used                   |

| 0x54   | Clear Interrupt               | No used                   |

| 0x60   | P1 COS Control                | No used                   |

| 0x64   | P2 COS Control                | No used                   |

| 0x68   | P3 COS Control                | No used                   |

| 0x6C   | P4 COS Control                | No used                   |

Table 3.1 Register Map

The PCI-7396 has 2/4 PPIs on board. Each PPI contains 5 registers, including Digital Data Register, Control Register, External Trigger Enable Register, External Trigger Disable Register, and COS Interrupt Control Register.

In the following sections, the 5 registers of PPI1 will be introduced respectively. The registers of the other 3 PPIs are of the same configuration which will not be repeated in this manual.

# 3.3 Digital Data Registers

The 24-bit I/O data of the PCI-7396 is accessed from/to this register by software. The digital data can also be read back through this register.

Address: BASE + 00h Attribute: read and write

Data Format:

| Bit          | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------------|-----|-----|-----|-----|-----|-----|-----|-----|

| BASE+        | P1A |

| 00h          | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| BASE+        | P1B |

| 01h          | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| BASE+        | P1C |

| 02h          | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| BASE+<br>03h | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

P1X7~P1X0: Digital I/O data X:A~C.

### 3.4 Control Register

Each PPI's control register is used to set its three ports to be as input or output one independently.

Address: BASE + 04h Attribute: write only Data Format:

| Bit       | 7 | 6 | 5 | 4 | 3 | 2   | 1   | 0   |

|-----------|---|---|---|---|---|-----|-----|-----|

| BASE+ 04h | Х | Х | Х | Х | Х | P1C | P1B | P1A |

| BASE+ 05h | Х | Х | х | Х | Х | Х   | Х   | Х   |

| BASE+ 06h | Х | Х | х | Х | Х | Х   | Х   | Х   |

| BASE+ 07h | х | х | х | х | х | Х   | Х   | Х   |

P1n: n: port number

Set to be '0' for input port, '1' for output port

# 3.5 External Trigger Enable Register

Users can write anything to this register to enable the external trigger to latch the input data of port A,B and C simultaneously. Note that when this register is enabled, the settings of the previous control register are disabled.

Address: BASE + 08h Attribute: write only Data Format:

| Bit      | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|---|---|---|---|---|---|---|---|

| BASE+08h | Х | Х | Х | Х | Х | Х | Х | Х |

| BASE+09h | Х | Х | Х | Х | Х | Х | Х | Х |

| BASE+0A  | Х | Х | х | Х | Х | Х | Х | х |

| h        |   |   |   |   |   |   |   |   |

| BASE+0B  | х | х | х | х | х | х | х | х |

| h        |   |   |   |   |   |   |   |   |

# 3.6 External Trigger Disable Register

Users can write anything to this register to disable the function of external trigger.

Address: BASE + 0Ch Attribute: write only Data Format:

| Bit          | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------------|---|---|---|---|---|---|---|---|

| BASE+0C<br>h | х | х | х | х | х | х | Х | х |

| BASE+0D<br>h | х | Х | Х | Х | Х | х | Х | Х |

| BASE+0E<br>h | х | Х | Х | х | Х | Х | Х | Х |

| BASE+0Fh     | Х | Х | Х | Х | Х | Х | Х | Х |

# 3.7 Change of State (COS) Control Register

This register is used to configure the COS interrupt.

Address: BASE + 60h Attribute: write only

Data Format:

| Bit      | 7 | 6 | 5 | 4 | 3 | 2   | 1   | 0   |

|----------|---|---|---|---|---|-----|-----|-----|

| BASE+60h | Х | Х | Х | Х | Х | P1C | P1B | P1A |

| BASE+61h | Х | Х | х | Х | Х | Х   | Х   | Х   |

| BASE+62h | Х | Х | Х | Х | Х | Х   | Х   | Х   |

| BASE+64h | Χ | х | х | х | х | х   | Х   | х   |

P1n: n: port number

Set to be '0' to disable COS, '1' to enable COS

## 3.8 Interrupt Source Control (ISC) Register

The PCI-7396 has a dual interrupt system, two interrupt sources can be generated and be distinguished by software setting. This register is used to select the interrupt sources.

Address: BASE + 50h Attribute: write only Data Format:

| Bit      | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|----------|---|---|---|---|-----|-----|-----|-----|

| BASE+50h | х | х | х | х | C2_ | C2_ | C1_ | C1_ |

|          |   |   |   |   | 1   | 0   | 1   | 0   |

| BASE+51h | Х | Х | х | Х | Х   | Х   | Х   | Х   |

| BASE+52h | Х | Х | Х | Х | Х   | Х   | Х   | Х   |

| BASE+54h | Х | Х | Х | Х | Х   | Х   | Х   | Х   |

C1\_0,C1\_1 : Select source INT 1 C2\_0,C2\_1 : Select source INT 2

| INT1   | C1_1 | C1_0 | IRQ Sources        | IRQ Trigger Condition                    |

|--------|------|------|--------------------|------------------------------------------|

| Mode 1 | 0    | 0    | COS P1&P2 (48bits) | Change of State for PCI-<br>7396 P1 & P2 |

| Mode 2 | 0    | 1    | P1C0 OR ~P1C3      | (see Table 4.2)                          |

| Mode 3 | 1    | 0    | ~P1C0              | falling edge of P1C0                     |

| Mode 4 | 1    | 1    | Event Counter      | Counter count down to 0                  |

| INT2   | C2_1 | C2_0 | IRQ Sources        | IRQ Trigger Condition                    |

| Mode 1 | 0    | 0    | COS P3&P4(48bits)  | Change of State for PCI-<br>7396 P3 & P4 |

| Mode 2 | 0    | 1    | P2C0 OR ~P2C3      | (see Table 4.2)                          |

| Mode 3 | 1    | 0    | ~P2C0              | falling edge of P2C0                     |

| Mode 4 | 1    | 1    | 32-bit Timer       | Timer count down to 0                    |

## 3.9 Clear Interrupt Register

Users can write anything to this register to clear the interrupt request of the PCI-7396.

Address: BASE + 54h Attribute: write only

Data Format:

| Bit      | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|---|---|---|---|---|---|---|---|

| BASE+54h | Χ | Х | Х | Х | Х | Х | Х | Х |

| BASE+55h | Х | Х | х | х | х | х | х | Х |

| BASE+56h | Х | Х | х | Х | Х | Х | Х | Х |

| BASE+57h | Х | Х | х | х | х | х | х | Х |

### 3.10 Timer/Counter Register

The 8254 chip occupies 4 I/O addresses in the PCI-7396. Please refer to NEC's or Intel's data sheet for the full description of the 8254 operation.

Address: BASE + 40h ~ BASE + 4Ch

Attribute : read / write

Data Format:

| Base + 40h | Bit 7~Bit 0: Counter 0 Register |

|------------|---------------------------------|

| Base + 44h | Bit 7~Bit 0: Counter 1 Register |

| Base + 48h | Bit 7~Bit 0: Counter 2 Register |

| Base + 4Ch | Bit 7~Bit 0: Control Register   |

# 3.11 High Level Programming

To operate the PCI-7396 quickly, you can bypass the detailed register structures and use the high-level application programming interface (API) directly. The DOS library for Borland C/C++ is included in the ADLINK CD. Please refer to chapter 5 for more detailed information.

# Operation Theorem

The operation theorem of the functions on PCI-7396 card is described in this chapter. The operation theorem can help you to understand how to manipulate or to program the PCI-7396.

## 4.1 Digital I/O Ports

#### 4.1.1 Introduction

The PCI-7396 has 2/4 PPIs on board. Each 24-bit PPI is divided into three 8-bit I/O ports: A, B, and C. All of these 6/12 ports can be programmed as input or output independent.

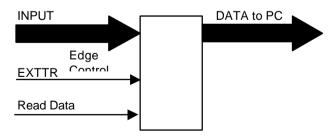

### 4.1.2 External Trigger

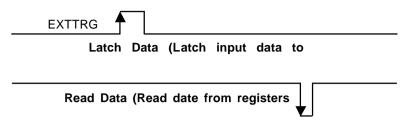

The pin-99 EXTTRG support user to receive an external trigger to latch input data. User can use function \_7396\_Set\_Event\_Edge to set EXTTRG pin to be active high or active low.

Figure 4.1 External Trigger Function Block

Figure 4.2 Read Data use External Trigger

### 4.2 8254 Timer/Counter Operation

#### 4.2.1 Introduction

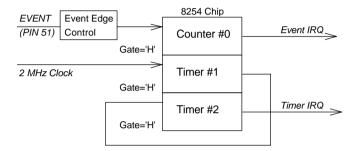

One 8254 programmable timer/counter chip is installed in the PCI-7396. There are three counters in one 8254 chip and 6 possible operation modes for each counter. The block diagram of the timer /counter system is shown in Figure 4.3.

Figure 4.3 Timer / counter system of PCI-7396.

Timer #1 and timer #2 of the 8254 chip are cascaded as a 32-bits programmable timer. In the software library, timer #1 and #2 are always set as mode 2 (rate generator). Counter #0 is used as an event counter, that is, there is an interrupt on the terminal count of 8254 mode 0.

#### 4.2.2 Cascaded 32 bits Timer

The base frequency of input clock for the cascaded timer is 2MHz. The output is send to be the timer interrupt. To set the maximum and minimum frequency of the timer, please refer to the function \_7348\_Cascaded\_Timer or \_7396\_Cascaded\_Timer.

### 4.2.3 Event Counter and Edge Control

The counter #0 of 8254 is used to be an event counter. The input is pin-51 of CN1. The trigger edge of counter clock is programmable. The gate control fixs high (enable). The output is send to be the event interrupt. That means If counter #0 is set as 8254 mode 0, the event IRQ asserts as the counter counts down to zero.

### 4.3 Interrupt Circuit

### 4.3.1 System Architecture

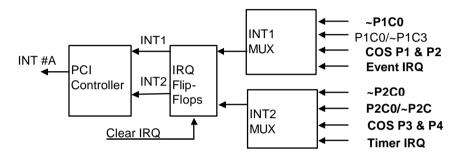

The PCI-7396's interrupt system is powerful and flexible, which is suitable for many applications. It is a *Dual Interrupt System*. The dual interrupt means the hardware can generate two interrupt request signals in the same time and the software can service these two request signals by ISR. Note that the dual interrupt do not mean the card occupy two IRQ levels.

The two interrupt request signals (INT1 and INT2) comes from digital inputs or the timer/counter outputs. Two multiplexers (MUX) are used to select the IRQ sources. Fig 4.4 shows the interrupt system.

### 4.3.2 IRQ Level Setting

There is only one IRQ level needed in the PCI-7396, although it is a dual interrupt system. This card uses INT #A interrupt request signal on PCI bus. The mother board circuits will transfer INT #A to one of the AT bus IRQ levels. The IRQ level is set by the PCI plug and play BIOS and saved in the PCI controller. It is not necessary for users to set the IRQ level. Users can get the IRQ level by software library.

### 4.3.3 Dual Interrupt System

The PCI controller can receive two hardware IRQ requests. However, only one IRQ will be sent to PCI bus, the two IRQ requests must be distinguished by user's interrupt service routine (ISR).

The two IRQ requests are named as INT1 and INT2. INT1 comes from COS P1 & P2, P1C0, P1C3, or the event counter interrupt. INT2 comes from COS P3 & P4, P2C0, P2C3, or the timer interrupt. The sources of INT1 and INT2 is selectable by using the Interrupt Source Control (ISC) Register.

Figure 4.4 Dual Interrupt System of PCI-7396

### 4.3.4 Interrupt Source Control (ISC)

There are four bits to control the IRQ sources of INT1 and INT2. Table 4.1 shows the selection of the IRQ sources and the interrupt trigger condition.

If the application needs one IRQ only, you can disable one of the IRQ sources by software. You can also disable both the two interrupts If you do not need any IRQ source. However, the PCI BIOS still assign a IRQ level to the PCI card and occupy the PC resource if you only disable the IRQ sources without change the initial condition of the PCI controller.

| INT1    | C1 | C2 | IRQ Sources        | IRQ Trigger Condition        |

|---------|----|----|--------------------|------------------------------|

| Disable | 4  | Χ  | INT1 disable       |                              |

| Mode 1  | 0  | Х  | COS P1&P2 (48bits) | Change of State for PCI-7396 |

| Mode 2  | 1  | Х  | P1C0 OR ~P1C3      | (see following)              |

| Mode 3  | 2  | Х  | ~P1C0              | falling edge of P1C0         |

| Mode 4  | 3  | Χ  | Event Counter      | Counter count down to 0      |

| INT2    | C1 | C2 | IRQ Sources        | IRQ Trigger Condition        |

| Disable | Χ  | 4  | INT2 disable       |                              |

| Mode 1  | X  | 0  | COS P3&P4 (48bits) | Change of State for PCI-7396 |

| Mode 2  | Χ  | 1  | P2C0 OR ~P2C3      | (see following)              |

| Mode 3  | Χ  | 2  | ~P2C0              | falling edge of P2C0         |

| Mode 4  | Υ  | 3  | Timer Output       | Timer count down to 0        |

Table 4.1 ISC register format

Default settings

When the IRQ sources is set as "P1C0 OR ~P1C3" or "P2C0 OR ~P2C3", the IRQ trigger conditions are summarized in Table 4.2,

| P1C0 | P1C3 | IRQ Trigger Condition                 |

|------|------|---------------------------------------|

| High | X    | P1C0='H' disable all IRQ              |

| Χ    | Low  | P1C3='L' disable all IRQ              |

| Low  | 1->0 | P1C3 falling edge trigger when P1C0=L |

| 0->1 | High | P1C0 rising edge trigger when P1C3=H  |

| P2C0 | P2C3 | IRQ Trigger Condition                 |

| High | Х    | P2C0='H' disable all IRQ              |

| Χ    | Low  | P2C3='L' disable all IRQ              |

| Low  | 1->0 | P2C3 falling edge trigger when P2C0=L |

| 0->1 | High | P2C0 rising edge trigger when P2C3=H  |

Table 4.2 IRQ Trigger conditions

By using the four signals: P1C0, P2C0, P1C3, and P2C3, user can utilize their combination to generate a proper IRQ for versatile applications.

### 4.3.5 Change of State (COS) Interrupt

#### What is COS?

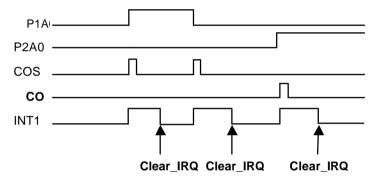

The COS (Change of State) means when the input state (logic level) is changed from low to high, or from high to low. The COS detection circuit will detect the edge of level change. In the PCI-7396 card, the COS detection circuit is applied to all the input channels. When any channel changes its logic level, the COS detection circuit generates an interrupt request to PCI controller.

#### **COS Detection**

The following timing is an example of COS operation. All the DI signals' level change will be detected and then take an 'OR' operation to generate the INT1 or INT2 IRQ request.

If INT1 or INT2 IRQ request generates, the signal will be latched. User should apply the function "\_7396\_CLR\_IRQ" or "\_7348\_CLR\_IRQ" to reset its state, after the corresponding ISR is finished,

## 4.4 12V and 5V Power Supply

The SCSI-100 connector CN1 provides +12V and +5V power supply (only for PCI-7348) for external devices. To avoid the short circuit or the overload of the power supply, the **resettable fuses** are added on all the power supply signals.

The maximum current for 5V power supply is 0.5 A. If the load current is larger than this limitation, the resistance of the resettable fuse will increase for the reason of the rising temperature. The rising resistance will further cause the power supply to reduce the load current. After the condition of overload or short circuit is removed, the fuse will return to its normal condition. It is unnecessary to replace the fuse.

The maximum current of 12V power supply is 0.5A, too. The action of the fuse is the same as that of +5V power supply.

5

## C/C++ Libraries

This chapter describes the software library for operating this card. Only the functions in DOS library and Windows 95 DLL are described. Please refer to the PCIS-DASK function reference manual, which included in ADLINK CD, for the descriptions of the Windows 98/NT/2000 DLL functions.

The function prototypes and some useful constants are defined in the header files LIB directory (DOS) and INCLUDE directory (Windows 95). For Windows 95 DLL, the developing environment can be Visual Basic 4.0 or above, Visual C/C++ 4.0 or above, Borland C++ 5.0 or above, Borland Delphi 2.x (32-bit) or above, or any Windows programming language that allows calls to a DLL. It provides the C/C++, VB, and Delphi include files.

## 5.1 Libraries Installation

Please refer to the "**Software Installation Guide**" for the detail information about how to install the software libraries for DOS, or Windows 95 DLL, or PCIS-DASK for Windows 98/NT/2000.

The device drivers and DLL functions of Windows 98/NT/2000 are included in the PCIS-DASK. Please refer the PCIS-DASK user's guide and function reference, which included in the ADLINK CD, for detailed programming information.

## 5.2 Programming Guide

#### 5.2.1 Naming Convention

The functions of the NuDAQ PCI cards or NuIPC CompactPCI cards' software driver are using full-names to represent the functions' real meaning. The naming convention rules are:

In DOS Environment:

```

{hardware model} {action name}. e.g. 7396 Initial().

```

In order to recognize the difference between DOS library and Windows 95 library, a capital "W" is put on the head of each function name of the Windows 95 DLL driver. e.g. w\_7396\_Initial().

#### 5.2.2 Data Types

We defined some data type in Pci\_7396.h (DOS) and Acl\_pci.h (Windows 95). These data types are used by NuDAQ Cards' library. We suggest you to use these data types in your application programs. The following table shows the data type names and their range.

| Type Name | Description                            | Range                                           |  |  |

|-----------|----------------------------------------|-------------------------------------------------|--|--|

| U8        | 8-bit ASCII character                  | 0 to 255                                        |  |  |

| l16       | 16-bit signed integer                  | -32768 to 32767                                 |  |  |

| U16       | 16-bit unsigned integer                | 0 to 65535                                      |  |  |

| 132       | 32-bit signed integer                  | -2147483648 to 2147483647                       |  |  |

| U32       | 32-bit single-precision floating-point | 0 to 4294967295                                 |  |  |

| F32       | 32-bit single-precision floating-point | -3.402823E38 to<br>3.402823E38                  |  |  |

| F64       | 64-bit double-precision floating-point | -1.797683134862315E308 to 1.797683134862315E309 |  |  |

| Boolean   | Boolean logic value                    | TRUE, FALSE                                     |  |  |

## 5.3 \_7396\_Initial

#### @ Description

This function is used to initialize the PCI-7396. Every PCI-7396 has to be initialized by this function before calling other functions.

#### @ Syntax

```

C/C++ (DOS)

U16 _7396_Initial (U16 *existCards, PCI_INFO *pciInfo)

C/C++ (Windows 95)

U16 W_7396_Initial (U16 *existCards, PCI_INFO *pciInfo)

Visual Basic (Windows 95)

W_7396_Initial (existCards As Integer, pciInfo As PCI_INFO) As Integer

```

#### @ Argument

existCards: The numbers of installed PCI-7396 cards. The

returned value shows how many PCI-7396 cards are

installed in your system.

pciinfo: It is a structure to memorize the PCI bus plug and

play initialization information which is decided by P&P BIOS. The PCI\_INFO structure is defined in ACL\_PCI.H. The base I/O address and the interrupt

channel number is stored in this variable.

#### @ Return Code

ERR NoError

ERR\_PCIBiosNotExist

## 5.4 7396 DI

#### @ Description

This function is used to read the 24-bit digital inputs data from the input port of the PCI-7396. The written data and read in data is 24 bits data. Each data is mapped to a signal as the table below.

| D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| PA7 | PA6 | PA5 | PA4 | PA3 | PA2 | PA1 | PA0 |

| D15 | D14 | D13 | D12 | D11 | D10 | D9  | D8  |

| PB7 | PB6 | PB5 | PB4 | PB3 | PB2 | PB1 | PB0 |

| D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 |

| PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 |

#### @ Syntax

```

C/C++ (DOS)

U16 _7396_DI (U16 cardNo, U16 channelPort, U32 *diData)

C/C++ (Windows 95)

U16 W 7396 DI (U16 cardNo, U16 channelPort, U32 *diData)

Visual Basic (Windows 95)

W 7396 DI (ByVal cardNo As Integer, ByVal channelPort As Integer,

diData As Integer) As Integer

```

```

@ Argument

cardNo: The card number of PCI7396 card initialized.

channelPort: port of each channel

P1_A : CH1's Port A

P1 B : CH1's Port B

P1 C : CH1's Port C

P1_ABC: CH1's Port A ,Port B ,Port C

P2_A : CH2's Port A

P2 B : CH2's Port B

P2_C : CH2's Port C

P2_ABC: CH2's Port A ,Port B ,Port C

(The following items are for PCI-7396 only.)

P3_A : CH3's Port A

P3 B : CH3's Port B

P3 C : CH3's Port C

P3_ABC: CH3's Port A ,Port B ,Port C

P4_A : CH4's Port A

P4 B : CH4's Port B

P4 C : CH4's Port C

P4_ABC: CH4's Port A ,Port B ,Port C

diData: returned 24-bit value from digital port.

```

| @ Return | Code |

|----------|------|

|----------|------|

## 5.5 7396 DO

#### @ Description

This function is used to write data to digital output ports. There are 6 ports (P1A, P1B, P1C, P2A, P2B, P2C) could be configured as digital outputs on the PCI-7348. And there are totally 12 digital output ports (P1A, P1B, P1C, P2A, P2B, P2C, P3A, P3B, P3C, P4A, P4B, P4C) could be configured as digital outputs on the PCI-7396.

#### @ Syntax

```

C/C++ (DOS)

U16 _7396_DO (U16 cardNo, U16 channelPort, U32 doData)

C/C++ (Windows 95)

U16 W_7396_DO (U16 cardNo, U16 channelPort, U32 doData)

Visual Basic (Windows 95)

W_7396_DO (ByVal cardNo As Integer, ByVal channelPort As Integer,

ByVal doData As Integer) As Integer

```

#### @ Argument

```

cardNo : The card number of PCI7396 card initialized. channelPort: The same as the arguments in the previous section. doData : value will be written to digital output port

```

#### @ Return Code

## 5.6 \_7396\_Config\_Port

#### @ Description

This function is used to configure the Input or Ouput of each Port. Each I/O Port of PCI-7396 is either input or output, so it has to configure as input or output before I/O operations are applied.

```

@ Syntax

```

```

C/C++ (DOS)

U16 _7396_Config_Port (U16 cardNo, int ctrlValue)

C/C++ (Windows 95)

U16 W 7396 Config Port (U16 cardNo, int ctrlValue)

Visual Basic (Windows 95)

W 7396 Config Port (ByVal cardNo As Integer, ByVal channelPort

As Integer, ByVal direction As Integer) As Integer

@ Argument

cardNo : The card number of PCI7396 card initialized.

ctrlValue :

Pland : CH1's Port A input port

P1BRD : CH1's Port B input port

P1CRD : CH1's Port C input port

P1RD : CH1's Port A,B,C input port

E P1RD : CH1's Port A,B,C input port use external clock to

latch data

PlawR : CH1's Port A output port

P1BWR : CH1's Port B output port

P1CWR : CH1's Port C output port

P1WR : CH1's Port A,B,C output port

P2ARD : CH2's Port A input port

P2BRD : CH2's Port B input port

P2CRD : CH2's Port C input port

P2RD : CH2's Port A,B,C input port

E P2RD : CH2's Port A,B,C input port use external clock

to latch data

P2AWR : CH2's Port A output port

P2BWR : CH2's Port B output port

P2CWR : CH2's Port C output port

P2WR : CH2's Port A,B,C output port

P3ARD : CH3's Port A input port

P3BRD : CH3's Port B input port

P3CRD : CH3's Port C input port

P3RD : CH3's Port A,B,C input port

E_P3RD : CH3's Port A,B,C input port use external clock to

latch data

P3AWR : CH3's Port A output port

P3BWR : CH3's Port B output port

```

P3CWR : CH3's Port C output port

P3WR : CH3's Port A,B,C output port

P4ARD : CH4's Port A input port

P4BRD : CH4's Port B input port

P4CRD : CH4's Port C input port

P4RD : CH4's Port A,B,C input port

E\_P4RD : CH4's Port A,B,C input port use external clock to

latch data

P4AWR : CH4's Port A output port

P4BWR : CH4's Port B output port

P4CWR : CH4's Port C output port

P4WR : CH4's Port A,B,C output port

#### @ Return Code

## 5.7 \_7396\_Software\_Reset

#### @ Description

This function is used to reset the I/O port configuration. After resetting PCI-7396, all ports will be set as input ones. Note that this function will not re-start the PCI bus and all the hardware settings will not be changed, neither.

#### @ Syntax

#### @ Return Code

## 5.8 \_7396\_INT\_Source\_Control

#### @ Description

The PCI-7396 has dual interrupts system, two interrupt sources can be generated and be checked by software. This function is used to select and control PCI-7396's interrupt sources by writing associated data to interrupt control register.

#### @ Syntax

```

C/C++ (DOS)

void _7396_INT_Source_Control (U16 cardNo, U16 c1, U16 c2)

C/C++ (Windows 95)

void W_7396_INT_Source_Control (U16 cardNo, U16 c1, U16 c2)

Visual Basic (Windows 95)

W_7396_INT_Source_Control (ByVal cardNo As Integer, ByVal c1 As Integer, ByVal c2 As Integer)

```

#### @ Argument

```

cardNo : The card number of PCI7396 card initialized.

c1 :INT1# interrupt source

c2 :INT2# interrupt source

For the C1,C2 settings, please refer to Table3.3.1

```

#### @ Return Code

## 5.9 \_7396\_COSIRQ\_Control

#### @ Description

This function is used to programe every channel port A,B,C's COS is enable or disable.

#### @ Syntax

```

C/C++ (DOS)

void _7396_COSIRQ_Control (U16 cardNo, int ch_no, int A, Int B,

int C)

C/C++ (Windows 95)

void W_7396_COSIRQ_Control (U16 cardNo, int ch_no, int A, Int B,

int C)

Visual Basic (Windows 95)

W_7396_COSIRQ_Control (ByVal cardNo As Integer, ByVal ch_no As

Integer, ByVal A As Integer, ByVal B As Integer, ByVal C As

Integer)

```

#### @ Argument

```

cardNo:The card number of PCI7396 card initialized.

ch_no :channel number set 1 or 2 or 3 or 4

A: port A control (enable set 1,disable set 0)

B: port B control (enable set 1,disable set 0)

C: port C control (enable set 1,disable set 0)

```

#### @ Return Code

## 5.10 \_7396\_CLR\_IRQ

### @ Description

This function is used to clear the interrupt request of PCI-7396.

#### @ Syntax

```

C/C++ (DOS)

void _7396_CLR_IRQ (U16 cardNo)

C/C++ (Windows 95)

void W_7396_CLR_IRQ (U16 cardNo)

Visual Basic(Windows 95)

W_7396_CLR_IRQ (ByVal cardNo As Integer)

```

#### @ Argument

cardNo : The card number of PCI7396 card initialized.

#### @ Return Code

None

## 5.11 \_7396\_Set\_Event\_Edge

#### @ Description

This function is used to set the edge trigger of event signal (Pin51) and external trigger signal (Pin99). The following table shows the possible settings.

| Set_Event_Edge C0        | 0                    | 1                     |

|--------------------------|----------------------|-----------------------|

| External Trigger (Pin99) | Active Low           | Active High           |

| Event (Pin51)            | Rising Edge<br>Count | Falling Edge<br>Count |

#### @ Syntax

```

C/C++ (DOS)

U16 _7396_Set_Event_Edge (U16 cardNo, U16 *c0)

C/C++ (Windows 95)

U16 W_7396_Set_Event_Edge (U16 cardNo, U16 *c0)

Visual Basic (Windows 95)

W_7396_ Set_Event_Edge (ByVal cardNo As Integer, c0 As Integer)

As Integer

```

#### @ Argument

cardNo :The card number of PCI7396 card initialized.

c0: The event signal and external clock signal setting.

#### @ Return Code

## 5.12 \_7396\_Cascaded\_Timer

#### @ Description

The function is used to program the timer#1 & timer#2 of 8254, the 32bit timer, to generate the timer interrupt .

#### @ Syntax

```

C/C++ (DOS)

U16 _7396_Cascaded_Timer (U16 *existCards, U16 c1, U16 c2)

C/C++ (Windows 95)

U16 W_7396_Cascaded_Timer (U16 *existCards, U16 c1, U16 c2)

Visual Basic (Windows 95)

W_7396_Initial (existCards As Integer, ByVal c1 As Integer,

ByVal c2 As Integer)

```

#### @ Argument

```

cardNo : The card number of PCI7396 card initialized.

c1 : frequency divider of timer #1

c2 : frequency divider of timer #2

About the settings of C1 & C2, please refer to section 3.2.2

```

#### @ Return Code

ERR\_NoError

ERR PCIBiosNotExist

## 5.13 \_7396\_Timer\_Start

#### @ Description

The function is used to program the timer#0 of 8254, 16bit timer, to generate the event interrupt .

#### @ Syntax

```

C/C++ (DOS, Windows 95)

U16 _7396_Timer_Start (U16 *existCards, U16 timer_mode, U16 c0)

C/C++ (DOS, Windows 95)

U16 W_7396_Timer_Start (U16 *existCards, U16 timer_mode, U16 c0)

Visual Basic (Windows 95)

W_7396_Initial (existCards As Integer, ByVal timer_mode As Integer, ByVal c0 As Integer)

```

#### @ Argument

```

cardNo: The card number of PCI7396 card initialized.

timer_mode: 8254 operating mode

c0: frequency divider of timer #0

```

#### @ Return Code

ERR\_NoError

ERR PCIBiosNotExist

## 5.14 \_7396\_Timer\_Read

#### @ Description

This function is used to read the counter value of the Counter#0.

#### @ Syntax

```

C/C++ (DOS)

U16 _7396_Timer_Read (U16 cardNo, U16 *c0)

C/C++ (Windows 95)

U16 W_7396_Timer_Read (U16 cardNo, U16 *c0)

Visual Basic (Windows 95)

W_7396_Timer_Read (ByVal cardNo As Integer, c0 As Integer) As Integer

```

#### @ Argument

```

cardNo : The card number of PCI7396 card initialized.

c0: count value of counter#0

```

#### @ Return Code

# Appendix 1 DIN-96DI

#### A1.1 Introductions

DIN-96DI digital input termination board features high-voltage opto-isolation on all inputs to prevent floating potential and ground loop problems from damaging your PC system. It is composed of one TB-96 base board, one TB-96DI daughter board, and one DIN socket for easy maintenance, wiring, and installation. It provides 96 channels that are accessed through a SCSI-100 connector.

#### A1.2 Features

- 96 Opto-Isolated digital input channels

- ♦ For use with the PCI-7396

- ◆ AC or DC polarity-free digital input

- Screw terminals for easy field wiring

## A1.3 Specifications

- Numbers of channel: 96

- Opto-isolator: PC3H4

- ◆ Input impedance: 4.7K Ohms

- ♦ Input voltage range: 0~24VDC

- ◆ Threshold voltage:

- 20VDC for 24V PS

- 8.8VDC for 12V PS

- 1.8VDC for 5V PS

- Isolation voltage: 2,500 Vdc channel-to-ground

- ◆ Connector: 100-Pin SCSI-type connector

- Dimensions: 112.7 mm x 225.0 mm

- ♦ Operating temp.: 0° ~ 60°C

- ♦ Storage temp.: -20° ~ 80°C

- ♦ Humidity: 5~95%, non-condensing

- ◆ Power consumption:

- 490mA(max.) for 24V PS

- 250mA(max.) for 12V PS

- 102mA(max.) for 5V PS

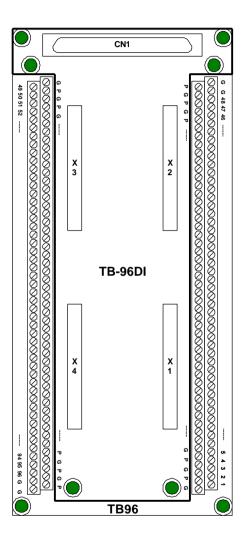

## A1.4 Layout of DIN-96DI

Legend:

CN1: SCSI II 100 pin connector to connect PCI-7396 and DIN-96DI X1~X4: 50 pin Opto-22 connectors to connect TB96 and Tb96DI

n(1~96): Input signal n G: External ground

P: External power (5~24V)

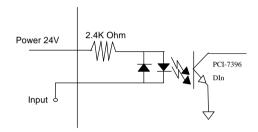

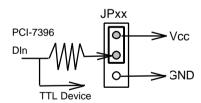

## A1.5 DI Circuits and Wiring

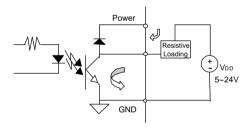

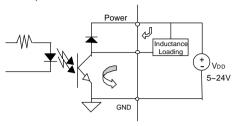

The outputs of the opto-isolated digital input circuits are open collector transistors. PCI-7396 should provide pull-high resistors by correct jumper setting. The connection between outside signal and PCI-7396 as well as the jumper setting are shown below.

Figure A1.1: opto-isolated input circuit

Figure A1.2: PCI-7396 jumper setting for DIN-96DI

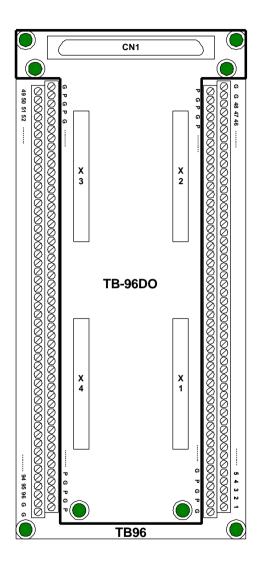

# Appendix 2 DIN-96DO

#### A2.1 Introductions

DIN-96DO digital output termination board features high-voltage optoisolation on all outputs to prevent floating potential and ground loop problems from damaging your PC system. It is composed of one TB-96 base board, one TB-96DO daughter board, and one DIN socket for easy maintenance, wiring, and installation. It provides 96 channels that are accessed through a SCSI-100 connector.

#### A2.2 Features

- 96 Opto-Isolated digital output channels

- ♦ For use with the PCI-7396

- On-board relay driver circuitry

- Screw terminals for easy field wiring

## A2.3 Specifications

- Numbers of channel: 96

- Opto-isolator: PC3H7